INPUT CON LETTORE TESSERE MAGNETICHE (RFID Reader)

Procuriamoci un RFID reader che permette la lettura di varie tessere magnetiche con Arduino.

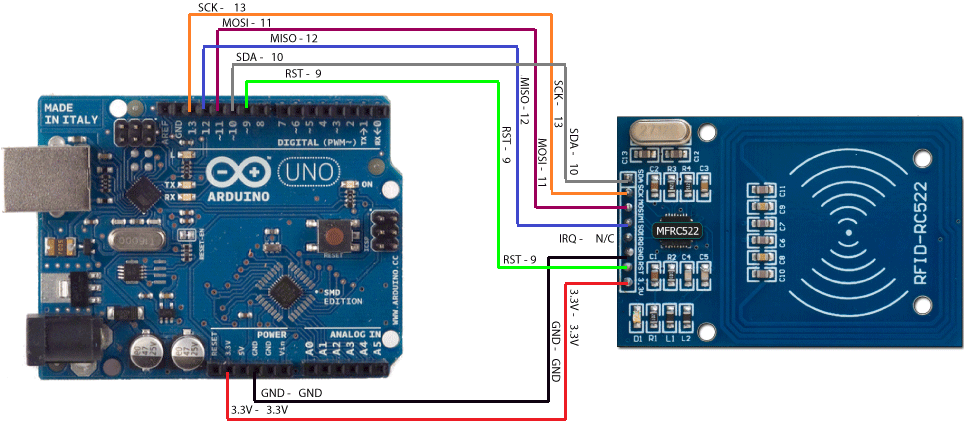

Colleghiamo il dispositivo seguendo lo schema indicato nella seguente figura.

Per rendere più semplice la scrittura del codice conviene scaricare la libreria ufficiale dell'RFID reader cliccando qui.

Il seguente programma permetta la lettura del codice di tessera magnetica, che viene passato sopra il dispositivo.

/* FILE: RC522_RFID DATE: 11/03/2017 VERSION: 0.1 Configurazione PIN RFID | Arduino ------+--------- SDA | D10 SCK | D13 MOSI | D11 MISO | D12 IRQ | N/A GND | GND RST | D9 3.3V | 3.3V ------+--------- */ #include#include /* Vengono definiti PIN del RFID reader*/ #define SDA_DIO 10 // 53 per Arduino Mega #define RESET_DIO 9 #define delayRead 1000 // Time of delay /* Viene creata una istanza della RFID libreria */ RFID RC522(SDA_DIO, RESET_DIO); void setup() { Serial.begin(9600); /* Abilita il canale seriale asincrono SPI*/ SPI.begin(); /* Viene inizilizzato RFID reader */ RC522.init(); } void loop() { byte i; // Se viene letta una tessera if (RC522.isCard()) { // Viene letto il suo codice RC522.readCardSerial(); Serial.println("Codice delle tessera letto:"); // Viene caricato il codice della tessera (composto da 5 byte) // all'interno di una Stringa String codiceLetto =""; for(i = 0; i <= 4; i++) codiceLetto+= String (RC522.serNum[i],HEX); codiceLetto.toUpperCase(); Serial.println(codiceLetto); delay(delayRead); } }

La sua esecuzione produce il seguente output sul monitor serial

Annotazioni (da http://it.emcelettronica.com/interfacce-seriali-meglio-spi-o-i2c ):

Le interfacce seriali sincrone sono caratterizzate dalla presenza di un segnale di sincronizzazione (clock) che determina la cadenza con cui i dati transitano attraverso il bus. Due tipici esempi di interfacce seriali sincrone sono appunto SPI (Serial Peripheral Interface) sviluppata da Motorola e I2C (Inter Integrated Circuits) sviluppata da Philips.

La comunicazione SPI prevede una periferica Master che comunica con diverse periferiche Slave e richiede un bus il cui numero di conduttori dipende dal numero di periferiche connesse. In particolare il bus è composto da 3+n fili (dove n è il numero di periferiche Slave). Il Master ha infatti una connessione dedicata per ciascuna periferica Slave (Slave Select) come si osserva in figura:

I segnali tipici di una comunicazione SPI sono i seguenti:

La distinzione tra le linee dati da (MISO) e verso (MOSI) le periferiche permette di ottenere una comunicazione full-duplex. Un dispositivo SPI possiede due bit di configurazione detti CPOL (ClockPOLarity) e CPHA (Clock PHAse).

CPOL determina lo stato idle del segnale di sincronismo: CPOL=0 significa che il segnale di clock è considerato idle quando è a livello logico basso. CPOL=1 significa che il segnale di clock è considerato idle quando è a livello logico alto.

CPHA determina invece su quale fronte del segnale di clock vengono letti i dati: con CPHA=0 i dati in uscita dal Master vengono letti in corrispondenza del fronte di discesa e i dati in uscita dagli Slave vengono letti in corrispondenza del fronte di salita del segnale di clock.

Disponendo di due bit di configurazione sono possibili quattro diverse modalità e due periferiche SPI connesse tra loro devono necessariamente utilizzare la stessa configurazione.

Le modalità di comunicazione SPI, determinate dalle impostazioni dei due bit di configurazione, sono riassunte nella tabella

| SPI MODE | CPOL | CPHA | CLK EDGE (CAMBIO

DATO) (dati in uscita dal master) |

CLK EDGE (ACQUISIZIONE DATO) (dati in uscita dalla periferica - in entrata per il master) |

| 0 | 0 | 0 | Discesa | Salita |

| 1 | 0 | 1 | Salita | Discesa |

| 2 | 1 | 0 | Salita | Discesa |

| 3 | 1 | 1 | Discesa | Salita |

Una comunicazione I2C si avvale di un bus seriale a due fili ed è sempre di tipo half-duplex. La struttura di un bus I2C è riportata nella figura seguente

I due segnali sono SCL (SerialCLock) e SDA (SerialDAta), sono entrambi bidirezionali. A differenza di una comunicazione SPI, I2C è una architettura multiMaster in cui la periferica che inizia la trasmissione e genera quindi il segnale di sincronismo è designata come Master, mentre la periferica oggetto della transazione indirizzata dal Master è considerata come Slave. Una periferica designata come Master per una certa trasmissione, potrà quindi essere anche uno Slave per una trasmissione successiva. I dati possono essere trasferiti a velocità massime di 100Kbps in modalità Standard, 400Kbps in modalità Fast e 3.4Mbps in modalità High-Speed. Nella modalità Standard gli Slave sono indirizzati con una modalità di indirizzamento a 7 bit, mentre nelle modalità Fast e High-Speed l’indirizzamento può essere a 7 o a 10 bit.

La comparazione tra le 2 modalità è riportata nella tabella sottostante:

| SPI | I2C |

| CONNESSIONE DELLE PERIFERICHE | |

| Le periferiche vengono connesse usando un minimo di tre fili e per questo motivo l’interfaccia SPI viene anche indicata come 3-wire interface. Le periferiche interconnesse condividono anche le stesse linee di alimentazione e, nel caso di più slave, è necessario disporre anche di un segnale /SS di abilitazione della singola periferica. Per la connessione di un master ed N periferiche slave sono quindi necessari 3+N fili oltre alle due linee di alimentazione. | Le periferiche vengono connesse tra loro mediante due fili. Il protocollo prevede l’indirizzamento delle periferiche mediante un identificativo a 7bit o 10bit (nel primo caso sono indirizzabili 27=128 periferiche mentre nel secondo caso 210=1024 periferiche). In nessuno dei due casi è richiesto un chip select. |

| VELOCITÀ DI COMUNICAZIONE | |

| La comunicazione dati in SPI può raggiungere anche i 10Mbps. Il grande vantaggio della comunicazione SPI in termini di velocità è la modalità full-duplex che consente lo scambio dati nelle due direzioni simultaneamente. | La comunicazione è half-duplex

e può raggiungere velocità massime diverse in base alla modalità di

trasmissione. In particolare: Standard mode:

max 100Kbps |

| ARCHITETTURA DI CONNESSIONE | |

| Architettura master-slave. In una comunicazione SPI è consentita la presenza di un solo master ed uno o più slave. Tuttavia è possibile implementare una architettura multimaster gestendo opportunamente via software le periferiche utilizzando il segnale /SS (Slave Select). | Architettura multimaster. Il protocollo prevede un sistema di arbitraggio basato su AND cablato che consente la gestione di conflitti generati dalla trasmissione dati contemporanea da parte di più periferiche. Per le caratteristiche dell’AND cablato, viene data priorità alla periferica che trasmette per prima uno zero logico. |

| IMMUNITÀ AL RUMORE | |

| La lettura/scrittura dati viene effettuata sul fronte di salita o di discesa del segnale di clock a seconda della modalità di comunicazione scelta. Questo aumenta fortemente l’immunità al rumore in quanto il dato viene campionato solamente per un breve periodo di tempo. | La comunicazione è level sensitive il che significa che il dato deve essere stabile per il tempo in cui il segnale di clock è attivo (livello alto). Minore è la velocità di comunicazione maggiore è tale intervallo di tempo tanto che un livello di rumore particolarmente elevato può compromettere il singolo bit provocando la transazione di una informazione errata. |

Conclusioni

Le interfacce seriali vengono usate con lo scopo di

minimizzare le interconnessioni e quindi per risparmiare le porte di I/O sul

microcontrollore.

Se l’applicazione prevede l’interconnessione di molti

dispositivi tra cui possono esservi più microcontrollori funzionanti come

Master, I2C diviene in questo caso una scelta obbligata. Se l’obiettivo è alta

velocità di trasmissione, basso costo ed alta immunità al rumore, allora la

scelta non può che ricadere su una interfaccia SPI, rinunciando però ad una

architettura multimaster e sacrificando qualche I/O in più sul vostro

microcontrollore.

I2C più lenta ma gestibile già con solo due I/O, mentre l’SPI più veloce ma con necessità di almeno 3 I/O.